1 Introduction

The TMS320C54xx is a cost-effective DSP family from TI that uses a high-performance, improved Harvard bus architecture; it includes a 40-bit arithmetic logic unit (including a 40-bit barrel shifter and two independent adders). Software programmable wait state generator and programmable partition conversion logic; an on-chip phase-locked loop (PLL) clock generator with an internal oscillator or an external clock source; this DSP with full-duplex serial port Supports 8-bit or 16-bit transfer; simultaneous with time-division multiplexed serial port, buffered serial port, 16-bit programmable timer, 8-bit parallel host interface, etc.; external bus can be used for shutdown control to disconnect external Data bus, address bus and control signals; the data bus has bus retention characteristics.

TI's TLV320AIC24 multimedia digital signal codec provides a time division multiplexed serial port (SMARTDM) and can synchronize the 4-wire serial port with an advanced TDM format to optimize DSP performance, thus enabling popular DSPs (such as C5000, C6000) and the seamless connection of the microcontroller. SMARTTDM provides continuous data conversion and reconfiguration programming modes (ADC/DAC and control data) to maximize the bandwidth of the TLV320AIC24DSP encoder and DSP data conversion (only for ADC/DAC data). In normal operation, it automatically finds the number of codes in the serial interface and adjusts the number of clocks to match the encoded data. In TURBO operation, it can maintain the same clock value, but the bit conversion rate reaches 25MHz at the maximum, allowing other DSP peripheral serial devices to separate the same serial bus in the same sampling period. The TLV320AIC24 supports any SMARTDM-based device cascading for multi-channel encoding (up to eight TLV320AIC24 encoding cascades to a single serial port). The three serial ports supported are single-master, single-slave, and cascaded. Master-slave mode.

The TLV320AIC24 also offers two 16-bit Σ-ΔA/D channels and 16-bit Σ-ΔD/A channels for connection to external devices such as cell phones, headphones, and microphones; embedded analog and digital sidetones, reverse bias filters Circuitry such as programmable input and output gain control provides preamplifier and 150Ω load for the microphone, hardware/software controlled power-down mode, etc. The TLV320AIC24 has a fully compatible power supply voltage to the TMS320C54xx; its programmable maximum sampling rate is 26ks/ s (with on-chip IIR/FIR filter) and 104ks/s (with IRR/FIR side-pass); their on-chip FIR produces 87dB of dynamic range (for ADC) and 92dB of dynamics at 8ks/s sampling rate Range (for DAC); ADC and DAC filters conform to the G.711 and G.722 protocols. In addition, the TLV320AIC24 provides a flexible host interface (a 2-bit serial port that can be programmed to the standard industrial I2C bus protocol or the S2C bus protocol).

2 hardware interface

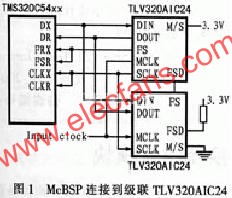

The interface between DSPMcBSP and TLV320AIC24 is four SMARTDM signals, which are frame synchronization, serial data output, serial data input and clock source, which are respectively connected to FSX/FSR, DR, DX, CLKX/CLKR. In cascade mode, the DSP can receive the frame sync signal through the FS terminal of the master device. The FDS terminal of the master device is connected to the FS terminal of the first-stage slave device, and the FSD terminal of the first-stage slave device is connected to the second-stage slave device. The FS side of the device, and so on. The last stage of the FSD is connected to the 3.3V power supply input via a resistor. Figure 1 shows the connection of the cascaded TLV320AIC24 to the DSP.

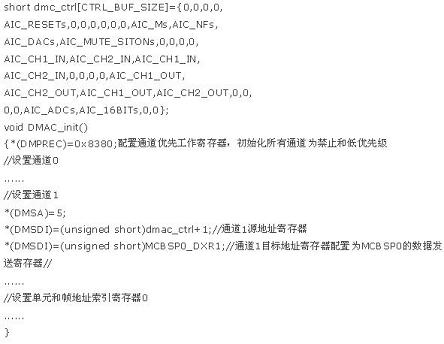

3 software programming

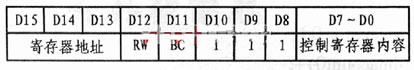

Each channel of the TLV320AIC24 contains six control registers that can be programmed to the desired mode of operation. In control frame mode, all registers can be programmed via the DIN pin. After a frame synchronization delay, the new configuration takes effect. After power-on, the TLV320AIC24 is defaulted to programming mode. Setting Control Register 1 to Bit 6 can be used to convert continuous data modes. If the 15+1 data format is used, then setting the lowest bit of DIN to 1 converts the continuous data transfer mode to the programmed mode. Its format is as follows:

Among them, the D15-D13 bit is the control register address, which can be written with the data carried by the bit D7-D0 during operation; the bit D12 is used to determine the reading and writing of the addressed register; the bit D11 is used to determine whether to select the broadcast mode. ; Bits D10-D8 are always set to 1.

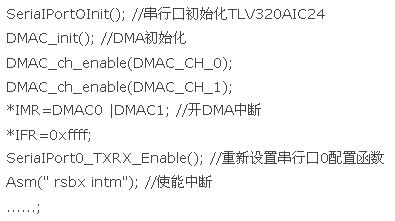

The programming example of the encoder register is given below. Among them, the DSP is connected to SMARTDM through DMA to initialize the TLV320AIC24. DMA refers to the technique of transmitting data in different intervals of a mapped memory area without CPU intervention. The DMA can support independent memory exchange between upper memory, on-chip peripherals (including EHPI8), or external devices without CPU.

(1) Initialization

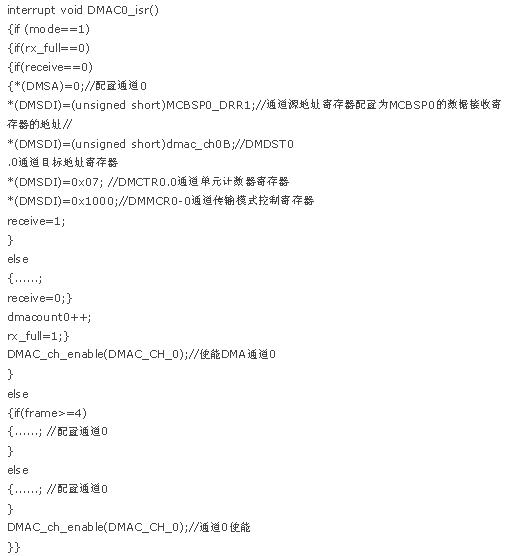

(2) DMA0 interrupt service subroutine for data reception

(3) Initialize the TLV320AIC24 subroutine with DMA

4 Conclusion

The hardware design method and software programming introduced in this paper can complete the acquisition and playback of voice signals, thus realizing the functions of voice data collection, processing and storage. The solution can meet the requirements of mainstream voice processing products and can be widely used in various related devices.

funcTIon ImgZoom(Id)//Reset the image size to prevent breaking the table { var w = $(Id).width; var m = 650; if(w< m){return;} else{ var h = $(Id) .height; $(Id).height = parseInt(h*m/w); $(Id).width = m; } } window.onload = funcTIon() { var Imgs = $("content").getElementsByTagName( "img"); var i=0; for(;i

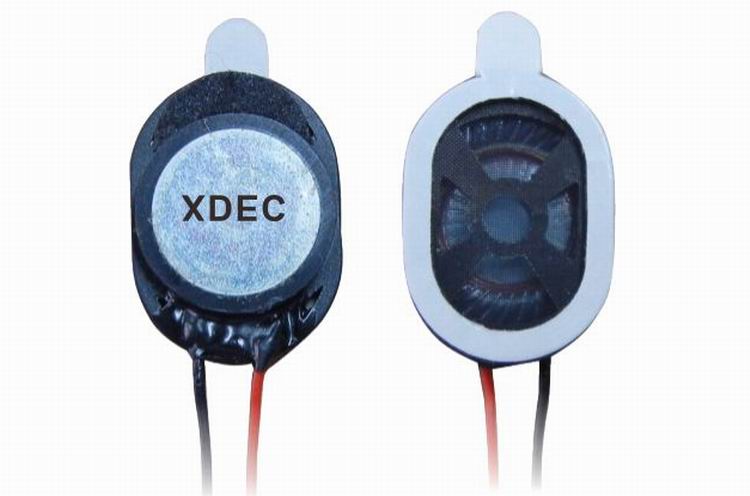

Tablet Speaker:

Tablet speaker is a kind of micro speaker unit which uses a diaphragm made of Mylar material. Mylar speakers are of ultrathin design and lightweight and clear voice. It is widely used mobile internet devices (tablet, notebook-).

There are two types of Mylar speakers from the shapes:

1) Round shapes, we have products from 10mm to 57mm in diameter.

2) Oblong shape, we have products in sizes of 1510/1712/1813-..

FAQ

Q1. What is the MOQ?

XDEC: 2000pcs for one model.

Q2. What is the delivery lead time?

XDEC: 15 days for normal orders, 10 days for urgent orders.

Q3. What are the payment methods?

XDEC: T/T, PayPal, Western Union, Money Gram.

Q4. Can you offer samples for testing?

XDEC: Yes, we offer free samples.

Q5. How soon can you send samples?

XDEC: We can send samples in 3-5 days.

Tablet Speaker

Tablet Speaker,Notebook Speaker,Laptop Speaker,Laptop Table Speaker

Shenzhen Xuanda Electronics Co., Ltd , http://www.xdecspeaker.com